## 1.0MHz,24V/2.0A High Performance, Boost Converter

## **General Description**

The LP6320C is a 1MHz PWM boost switching designed for constant-voltage regulator applications. The LP6230C can drive a string of up to 30V. The LP6230C implements a constant frequency 1MHz PWM control scheme. The high frequency PWM operation also saves board space by reducing external component sizes. The LP6230C features automatic shifting to pulse frequency modulation mode at light loads. Highly integration and internal compensation network minimizes as 6 external component counts. Optimized operation frequency can requirement of small LC filters value and low operation current with high efficiency. The LP6230C includes under-voltage lockout, current limiting, and thermal overload protection to prevent damage in the event of an output overload. The LP6230A is available in a small 8-pin MSOP8 package.

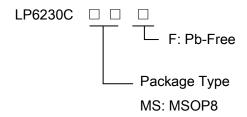

## Order Information

## **Applications**

- Panel Bias Voltage supply

- OLED Backlight driver

- Portable Applications

- MID/PTV

### **Features**

- High Efficiency: 90%

- 1MHzFixed-Frequency PWM Operation

- Maximum Output Voltage up to 24V

- Guaranteed 13V/200mA Output with 5V input

- Operating Range: 2.2V to 6V

- Shutdown Supply Current:<1uA

- Minimize the External Component

- RoHS Compliant and 100% Lead(Pb)-Free

- Available in MSOP8 Package

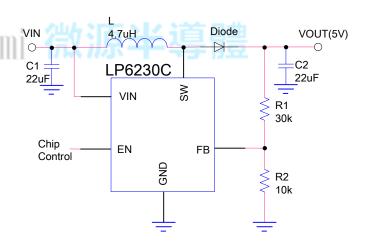

# **Typical Application Circuit**

## **Marking Information**

| Device  | Marking | Package | Shipping |

|---------|---------|---------|----------|

| LP6230C |         | MSOP8   | 3K/REEL  |

|         |         |         |          |

www.lowpowersemi.com

LP6230C Jun.-2014 Email: marketing@lowpowersemi.com

# **Functional Pin Description**

| Pack  | rage Type | Pin Configurations                                                                                                                                                              |                      |  |

|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| M     | 1SOP8     | NC 1 FB 2 EN 3 GND 4                                                                                                                                                            | 8 NC 7 NC 6 VIN 5 SW |  |

| Pin   | Name      | Description                                                                                                                                                                     |                      |  |

| 1,7,8 | NC        | No Connector.                                                                                                                                                                   |                      |  |

| 2     | FB        | Regulation Feedback Input. Connect to an external resistive voltage divider from the output to FB to set the output voltage.                                                    |                      |  |

| 3     | EN        | Regulator ON/OFF Control Input. A logic high input( $V_{EN}>1.4V$ ) turns on the regulator. A logic low input( $V_{EN}<0.4V$ ) puts the LP6230C into low current shutdown mode. |                      |  |

| 4     | GND       | Ground.                                                                                                                                                                         |                      |  |

| 5     | SW        | Switching pin.                                                                                                                                                                  |                      |  |

| 6     | VIN       | Power Supply pin.                                                                                                                                                               |                      |  |

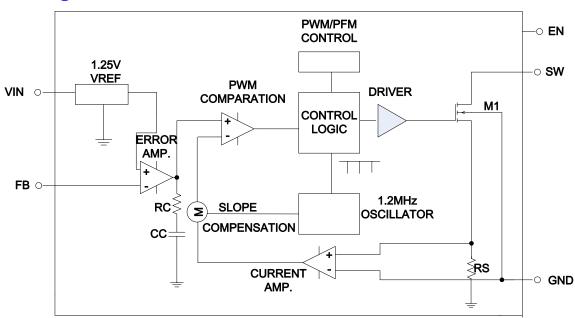

## **Function Diagram**

LowPowerSemi 微源半導體

LP6230C Jun.-2014 Email: <a href="marketing@lowpowersemi.com">marketing@lowpowersemi.com</a> www.lowpowersemi.com Page 2 of 7

# **Preliminary Datasheet**

**LP6230C**

# **Absolute Maximum Ratings** Note 1

| $\diamond$     | VIN to GND                                       | 0.3V to 6.5V |

|----------------|--------------------------------------------------|--------------|

| $\diamond$     | SW to GND                                        | 0.3V to 30V  |

| $\diamondsuit$ | Other Pin to GND                                 | 0.3V to 6V   |

| $\diamond$     | Maximum Junction Temperature                     | 150°C        |

| $\diamond$     | Operating Ambient Temperature Range              | 20°C to 85°C |

| <b></b>        | Maximum Soldering Temperature (at leads, 10 sec) | 260°C        |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Information**

- $\label{eq:maximum} \Leftrightarrow \quad \text{Maximum Power Dissipation (MSOP8,PD,T_A=25°C)} \quad ------ \quad 900 \text{mW}$

- $\Leftrightarrow$  Thermal Resistance ( $\theta_{JA}$ ) ------ 165°C/W

## **ESD Susceptibility**

- ♦ HBM(Human Body Mode) ------ 2KV

- ♦ MM(Machine Mode) ------ 200V

## **Electrical Characteristics**

$(V_{IN}=3.5V, V_{OUT}=5V, C_{IN}=10uF, C_{OUT}=22uF, L_1=4.7uH, R_1=30K, R_2=10K)$

| Parameter                   | Symbol               | Condition             | Min  | Тур  | Max  | Units |

|-----------------------------|----------------------|-----------------------|------|------|------|-------|

| Operation voltage Range     | V <sub>IN</sub>      |                       | 2.2  |      | 6    | ٧     |

| Input Under Voltage Lockout | UVLO                 |                       |      | 2.0  |      | V     |

| UVLO Hysteresis Voltage     |                      |                       |      | 0.2  |      | ٧     |

| Supply Current              | ΙQ                   | V <sub>FB</sub> =1.3V |      | 100  |      | μΑ    |

| Shut Down Current           | I <sub>SD</sub>      | V <sub>EN</sub> =0V   |      | 0.1  | 1    | μΑ    |

| Operation Frequency         | f <sub>OSC</sub>     |                       |      | 1.0  |      | MHz   |

| Maximum Duty Cycle          |                      |                       | 93   |      |      | %     |

| Feedback Voltage            | $V_{FB}$             |                       | 1.22 | 1.25 | 1.28 | ٧     |

| On Resistance of MOSFET     | R <sub>DS(ON)</sub>  |                       |      | 0.3  |      | Ω     |

| SW Current Limit            | I <sub>LM</sub>      |                       |      | 2    |      | Α     |

| Shut Down Voltage           | V <sub>EN(OFF)</sub> |                       |      |      | 0.4  | V     |

| Enable on Voltage           | V <sub>EN(ON)</sub>  |                       | 1.4  |      |      | V     |

LP6230C Jun.-2014

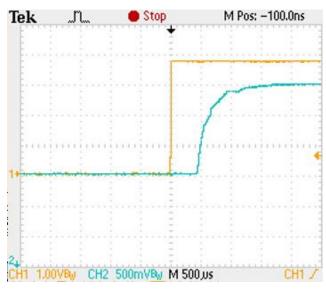

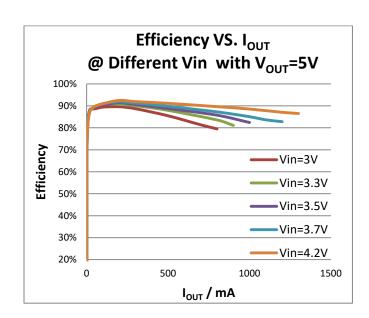

# **Typical Operating Characteristics**

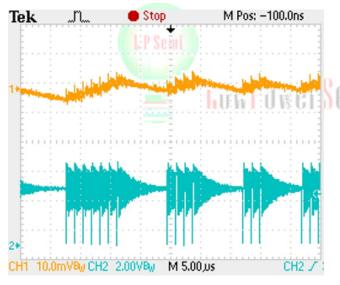

Start up Waveform  $CH_1=V_{EN}$ ,  $CH_2=V_{OUT}$

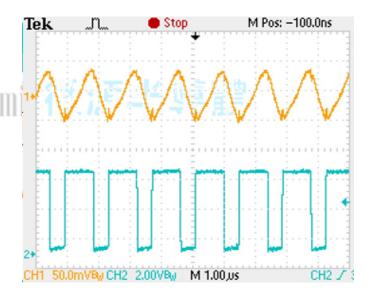

$CH_1 = \triangle V_{OUT}$ ,  $CH_2 = V_{SW}$  @  $V_{IN} = 3.7V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 1mA$

$CH_1 = \triangle V_{OUT}, \;\; CH_2 = V_{SW} \; @ \; V_{IN} = 3.7V, \; V_{OUT} = 5V, \; I_{OUT} = 500 mA$

LP6230C

Jun.-2014

Email: marketing@lowpowersemi.com

## **Operation Information**

The LP6230C uses a fixed frequency, peak current mode boost regulator architecture to regulate voltage at the feedback pin. At the start of each oscillator cycle the MOSFET is turned on through the control circuitry. To prevent sub-harmonic oscillations at duty cycles greater than 50 percent, a stabilizing ramp is added to the output of the current sense amplifier and the result is fed into the negative input of the PWM comparator. When this voltage equals The output voltage of the error amplifier the power MOSFET is turned off. The voltage at the output of the error amplifier is an amplified version of the difference between the 1.25V bandgap reference voltage and the feedback voltage. In this way the peak current level keeps the output in regulation. If the feedback voltage starts to drop, the output of the error amplifier increases. These results in more current to flow through the power MOSFET, thus increasing the power delivered to the output. TheLP6230C has internal soft start to limit the amount of input current at startup and to also limit the amount of overshoot on the output.

#### Setting the Output Voltage

Set the output voltage by selecting the resistive voltage divider ratio. The voltage divider drops the output voltage to the 1.25V feedback voltage. Use a 100K resistor for R<sub>2</sub> of the voltage divider. Determine the high-side resistor  $R_1$  by the equation:

$$V_{OUT} = (R_1 / R_2 + 1) \times V_{FB}$$

#### **Current Limitation**

The internal power-MOS switch current is monitored cycle-by-cycle and is limited to the value not exceed 2.0A(Typ.). When the switch current reaches the limited value, the internal power-MOS is turned off immediately until the next cycle.

#### **Inductor Selection**

For a better efficiency in high switching frequency converter, the inductor selection has to use a proper core material such as ferrite core to reduce the core loss and choose low ESR wire to reduce copper loss. The most important point is to prevent the core saturated when handling the maximum peak current. Using a shielded inductor can minimize radiated noise in sensitive applications. The maximum peak inductor current is the maximum input current plus the half of inductor ripple current. The calculated peak current has to be smaller than the current limitation in the electrical characteristics. A typical setting of the inductor ripple current is 20% to 40% of the maximum input current. If the selection is 40%, the maximum peak inductor current is

$$\begin{split} I_{PEAK} &= I_{IN(MAX)} + \frac{1}{2}I_{RIPPLE} = 1.2 \times I_{IN(MAX)} \\ &= 1.2 \times \left\lceil \frac{I_{OUT(MAX)} \times V_{OUT}}{\eta \times V_{IN(MIN)}} \right\rceil \end{split}$$

The minimum inductance value is derived from the following equation:

$$L = \frac{\eta \times V_{IN(MIN)}^2 \times \left[V_{OUT} - V_{IN(MIN)}\right]}{0.4 \times I_{OUT(MAX)} \times V_{OUT}^2 \times f_{OSC}}$$

Depending on the application, the recommended inductor value is between 2.2µH to 10µH.

LP6230C Jun.-2014 Email: marketing@lowpowersemi.com

### **Diode Selection**

To achieve high efficiency, Schottky diode is good choice for low forward drop voltage and fast switching time. The output diode rating should be able to handle the maximum output voltage, average power dissipation and the pulsating diode peak current.

### **Input Capacitor Selection**

For better input bypassing, low-ESR ceramic capacitors are recommended for performance. A 10µF input capacitor is sufficient for most applications. For a lower output power requirement application, this value can be decreased.

### **Output Capacitor Selection**

For lower output voltage ripple, low-ESR ceramic capacitors are recommended. The tantalum capacitors can be used as well, but the ESR is bigger than ceramic capacitor. The output voltage ripple consists of two components: one is the pulsating output ripple current flows through the ESR, and the other is the capacitive ripple caused by charging and discharging.

$$V_{RIPPLE} = V_{RIPPLE\_ESR} + V_{RIPPLE\_C}$$

$$\cong I_{PEAK} \times R_{ESR} + \frac{I_{PEAK}}{C_{OUT}} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT} \times f_{OSC}} \right)$$

### **Layout Guideline**

For high frequency switching power supplies, the PCB layout is important step in system application design. In order to let IC achieve good regulation, high efficiency and stability, it is strongly recommended the power components should be placed as close as possible. The set races should be wide and short. The feedback pin and then works of feedback and compensation should keep away from the power loops, and be shielded with a ground trace or plane to prevent noise coupling. Input and Output capacitors should be placed close to the IC and connected to ground plane to reduce noise coupling.

LP6230C

Jun.-2014

4 Email

Email: marketing@lowpowersemi.com

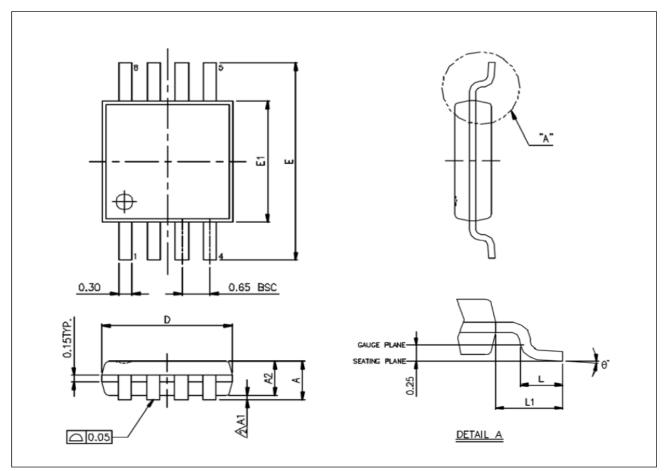

# **Packaging Information**

### MSOP-8L

Unit: mm

| Symbols | Min. (mm) | Max. (mm) |  |

|---------|-----------|-----------|--|

| Α       |           | 1.100     |  |

| A1      | 0.000     | 0.150     |  |

| A2      | 0.750     | 0.950     |  |

| D       | 3.000 BSC |           |  |

| E       | 4.900 BSC |           |  |

| E1      | 3.000 BSC |           |  |

| L       | 0.400     | 0.800     |  |

| L1      | 0.950 REF |           |  |

| θ°      | 0° 8°     |           |  |

### Note:

- Package dimensions are in compliance with JEDEC outline: MO-187 AA.

- 2. Dimension "D" does not include molding flash, protrusions or gate burrs.

- Dimension "E1" does not include inter-lead flash or protrusions.

LP6230C Jun.-2014 Email: marketing@lowpowersemi.com www.lowpowersemi.com